集成運算放大電路在現代軟件開發中的基礎性應用(2021年2月7日)

在2021年2月7日這個看似普通的時間節點,探討“集成運算放大電路”與“軟件開發”這兩個看似分屬硬件與軟件領域的主題,似乎有些跨越。在現代技術高度融合的背景下,這種關聯并非牽強。集成運算放大器(Op-Amp)作為模擬電路的核心基石,其原理與應用正以深刻而間接的方式,持續影響著軟件開發的進程與邊界。

從技術生態的宏觀視角看,集成運放是幾乎所有現代電子設備,從智能手機、數據中心服務器到工業控制器的物理基礎。軟件開發,尤其是系統級、嵌入式、物聯網(IoT)和人工智能邊緣計算領域的開發,最終都運行在這些由模擬與數字電路構成的硬件平臺上。2021年,隨著5G、IoT和AI的深入發展,對低功耗、高精度信號處理的需求激增,這直接驅動了集成運放設計(如低噪聲、低失調、高帶寬產品)的進步。軟件開發者在設計算法(如傳感器數據濾波、音頻處理、圖像信號前端處理算法)時,必須理解其底層硬件——包括運放——的特性與局限。一個高效的軟件算法,往往需要與硬件特性(如運放的增益帶寬積、壓擺率)協同設計,才能發揮最大效能。

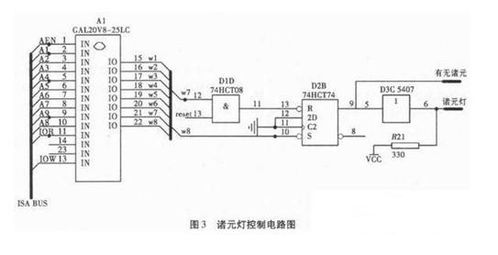

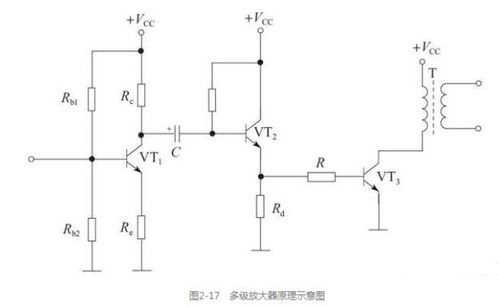

在開發工具與仿真環節,集成運放知識至關重要。許多用于控制系統設計、信號處理算法原型開發的軟件工具(如MATLAB/Simulink、LTspice、PSpice)都內置了豐富的運放模型。軟件開發人員,特別是算法工程師和嵌入式軟件工程師,經常需要使用這些工具進行建模和仿真,以驗證算法在接近真實物理環境中的表現。例如,設計一個用于醫療設備的心電信號采集軟件,開發者必須在仿真中考慮運放帶來的噪聲、漂移和帶寬限制,從而在軟件中設計相應的數字濾波和校準算法。因此,對集成運放電路的理解,能幫助開發者更準確地進行軟件建模,減少后期硬件聯調的成本與風險。

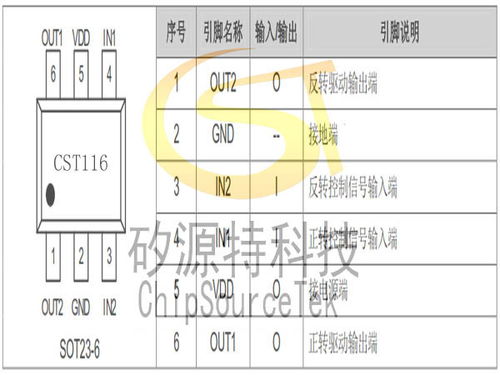

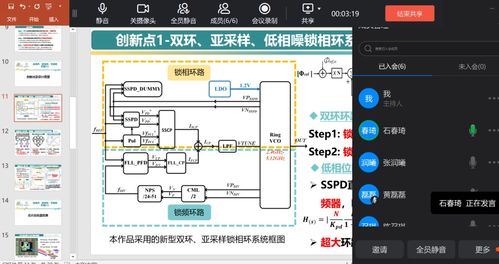

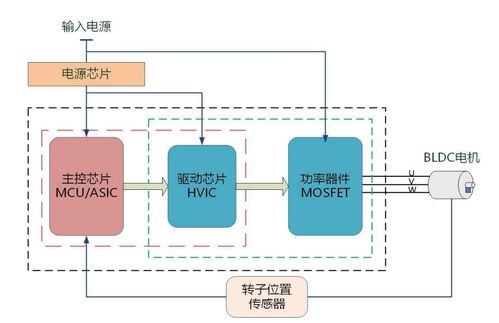

隨著硬件抽象層的提高和“軟件定義一切”的趨勢,集成運放的功能正越來越多地通過可編程邏輯和軟件來實現。例如,在軟件定義無線電(SDR)或某些數字信號處理(DSP)應用中,傳統由模擬運放完成的放大、濾波功能,可以通過高性能ADC/DAC配合軟件算法在數字域實現。開發這類軟件,要求開發者不僅精通編程,還需深刻理解運放所代表的模擬信號處理原理,才能設計出等效甚至性能更優的數字替代方案。這標志著軟件開發深度融入了傳統硬件領域。

在教育和思維訓練層面,集成運放所體現的負反饋、虛短虛斷、穩定性分析等核心思想,是一種精妙的系統控制與設計哲學。這種嚴謹的、基于模型的分析方法,對培養軟件開發人員的系統思維、調試能力和對性能邊界的洞察力大有裨益。在2021年,面對日益復雜的軟件系統,這種底層硬件賦予的工程化思維顯得尤為珍貴。

2021年2月7日,當我們聚焦軟件開發時,集成運算放大電路并非一個遙遠的硬件名詞。它是物理世界與數字世界交互的關鍵接口,是高級開發工具中的核心模型,是算法設計必須考量的約束條件,更是一種寶貴的工程思維源泉。在軟硬件協同設計成為主流的時代,一位對集成運放原理有清晰認識的軟件開發者,往往能設計出更穩健、高效且與硬件完美契合的軟件解決方案。

如若轉載,請注明出處:http://www.mediatemple.com.cn/product/51.html

更新時間:2026-04-08 08:07:32