電子電氣架構中SoC設計流程及其集成開發(fā)環(huán)境與集成電路設計服務

隨著信息技術的快速發(fā)展,系統(tǒng)級芯片(SoC)在電子電氣架構中扮演著核心角色,廣泛應用于汽車電子、物聯(lián)網和消費電子等領域。SoC設計流程復雜,涉及多個階段,并高度依賴先進的集成開發(fā)環(huán)境(IDE)和專業(yè)的集成電路設計服務。本文將詳細介紹SoC設計流程、關鍵集成開發(fā)環(huán)境以及集成電路設計服務的主要內容,以幫助讀者全面理解這一領域。

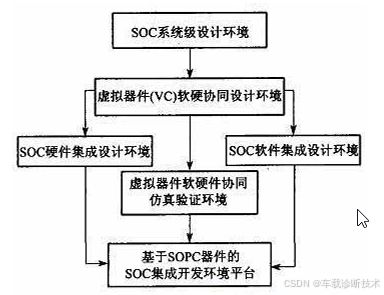

一、SoC設計流程

SoC設計流程通常包括多個階段,從概念定義到最終產品實現,具體如下:

1. 需求分析與規(guī)格定義:根據應用場景,明確SoC的功能、性能、功耗和成本等要求。例如,在汽車電子中,需考慮實時性和可靠性。

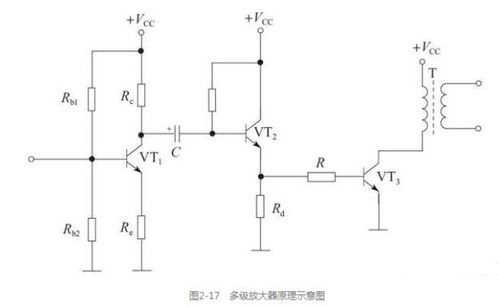

2. 架構設計:確定SoC的整體架構,包括處理器核心、內存、外設接口和通信總線等組件的布局。這階段需要平衡性能和面積約束。

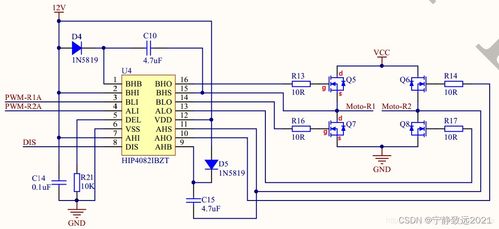

3. 硬件設計:包括寄存器傳輸級(RTL)設計、邏輯綜合和物理設計。使用硬件描述語言(如Verilog或VHDL)進行RTL編碼,然后通過綜合工具將代碼轉換為門級網表,最終進行布局布線。

4. 軟件設計:并行開發(fā)固件、驅動程序和操作系統(tǒng),確保軟硬件協(xié)同工作。這通常涉及嵌入式軟件開發(fā)。

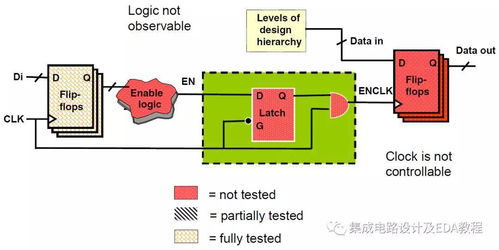

5. 驗證與測試:通過仿真、形式驗證和原型測試,確保SoC功能正確。驗證階段可能占用整個設計周期的50%以上時間。

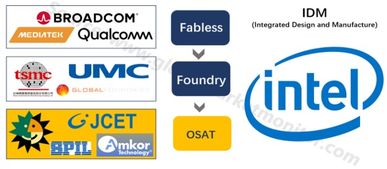

6. 制造與封裝:將設計交付給代工廠進行晶圓制造,然后進行封裝和測試,形成最終芯片。

整個流程強調迭代和優(yōu)化,以應對日益增長的復雜度和時間壓力。

二、集成開發(fā)環(huán)境(IDE)在SoC設計中的作用

集成開發(fā)環(huán)境是SoC設計的核心工具集,提供一體化的開發(fā)、調試和驗證平臺。主要功能包括:

- 代碼編輯與編譯:支持硬件和軟件代碼的編寫、編譯和優(yōu)化,例如使用Eclipse-based IDE或專用工具如Cadence Virtuoso。

- 仿真與調試:通過仿真器(如ModelSim)和調試器進行功能驗證,幫助識別設計錯誤。

- 性能分析:集成性能監(jiān)控工具,分析功耗、時序和面積,輔助設計優(yōu)化。

- 協(xié)同開發(fā):支持團隊協(xié)作,集成版本控制系統(tǒng)(如Git),提高開發(fā)效率。

常見的SoC IDE包括Arm DS-5、Xilinx Vivado和Synopsys Platform Architect等,這些工具通過自動化流程減少人為錯誤,加速產品上市。

三、集成電路設計服務的角色

隨著SoC復雜度增加,許多企業(yè)依賴專業(yè)的集成電路設計服務來補充內部資源。這些服務涵蓋:

- 設計咨詢與架構規(guī)劃:提供專家建議,優(yōu)化SoC架構以滿足特定應用需求。

- IP核集成:集成預驗證的知識產權(IP)核,如處理器、存儲器接口,縮短開發(fā)周期。

- 外包設計與驗證:承接部分或全部設計任務,包括RTL編碼、綜合和驗證,降低成本風險。

- 制造支持:協(xié)助與代工廠溝通,處理工藝相關問題和測試方案。

設計服務提供商如臺積電設計服務聯(lián)盟或獨立設計公司,幫助客戶應對技術挑戰(zhàn),提升產品競爭力。

四、總結與展望

SoC設計流程的嚴謹性、集成開發(fā)環(huán)境的先進性以及集成電路設計服務的專業(yè)化,共同推動了電子電氣架構的創(chuàng)新。隨著人工智能和5G技術的普及,SoC設計將更注重能效和安全性,開發(fā)環(huán)境將集成更多AI輔助工具,設計服務也將向云化和定制化發(fā)展。企業(yè)和工程師應持續(xù)關注這些趨勢,以在競爭激烈的市場中保持領先。

如若轉載,請注明出處:http://www.mediatemple.com.cn/product/36.html

更新時間:2026-04-08 09:27:38